Example layout patterns for characterizing layout effects: (a) Poly-... | Download Scientific Diagram

Modified transistor layout to study poly-pitch effect and LOD effect... | Download Scientific Diagram

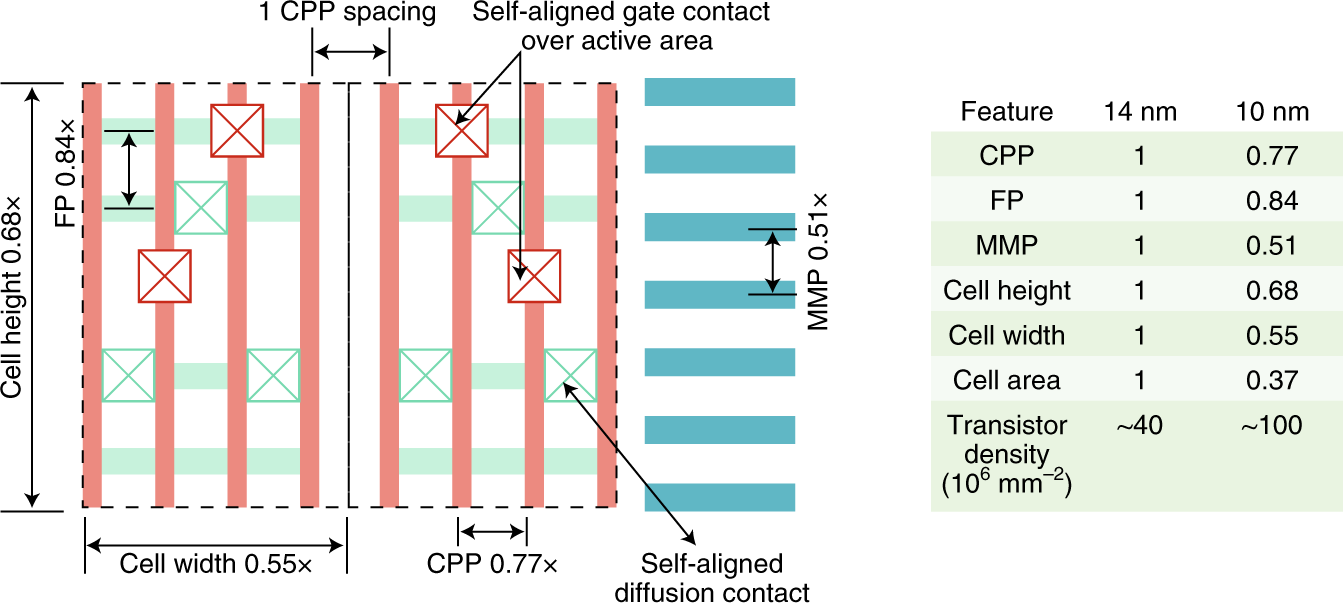

Figure A.2: Scaling metrics; a. Metal pitch; b. Gate-length; c. Flash... | Download Scientific Diagram

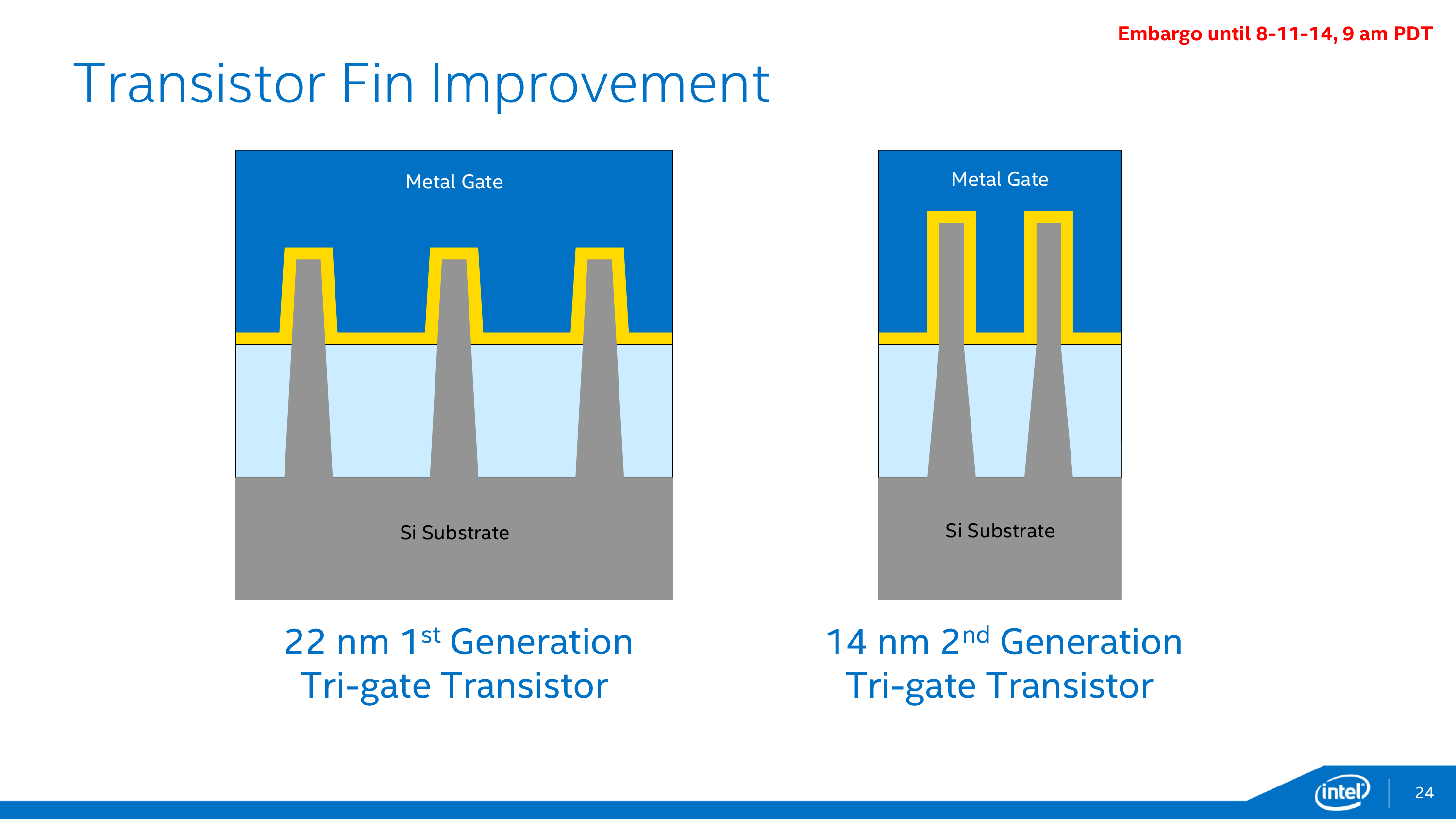

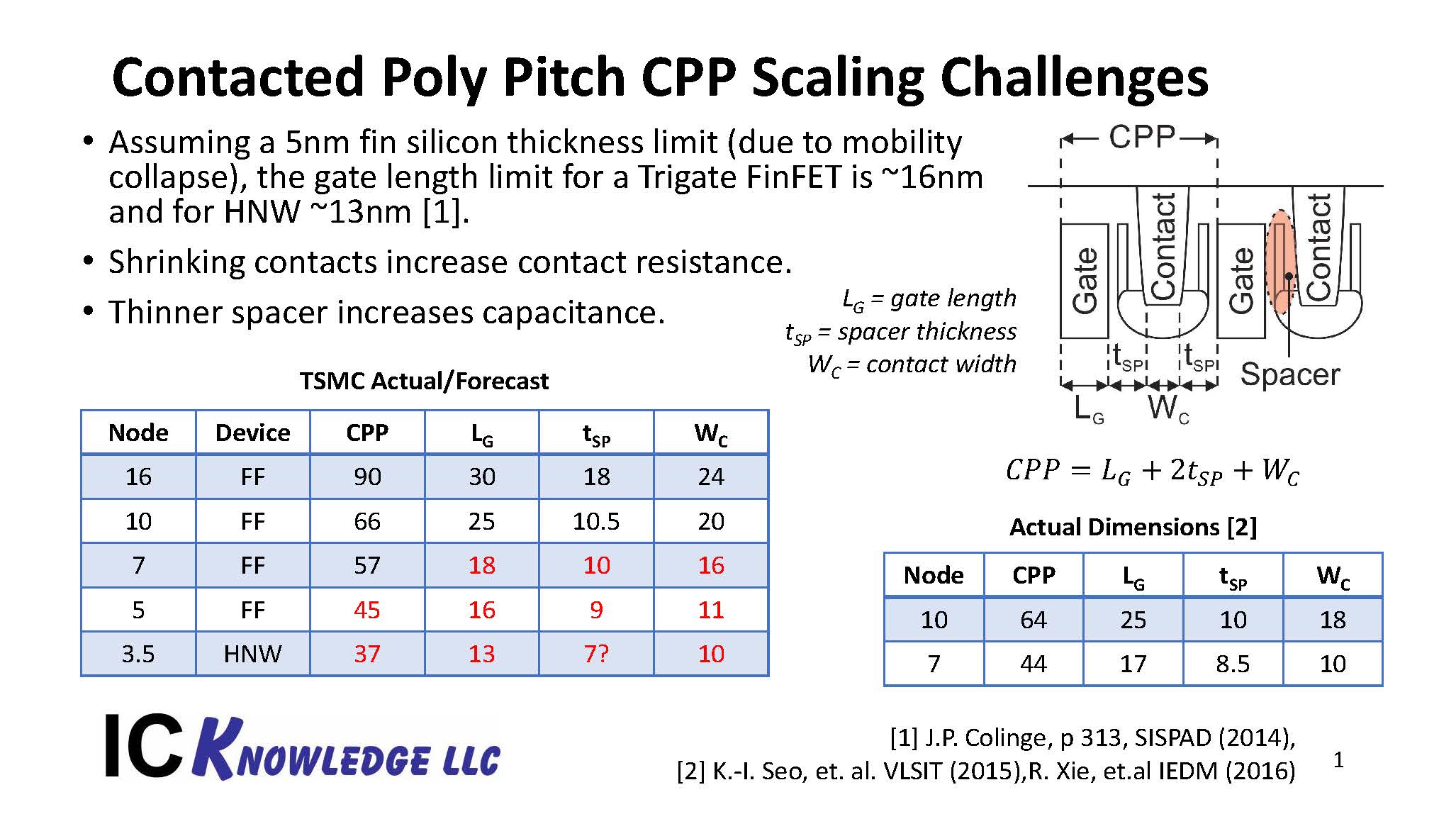

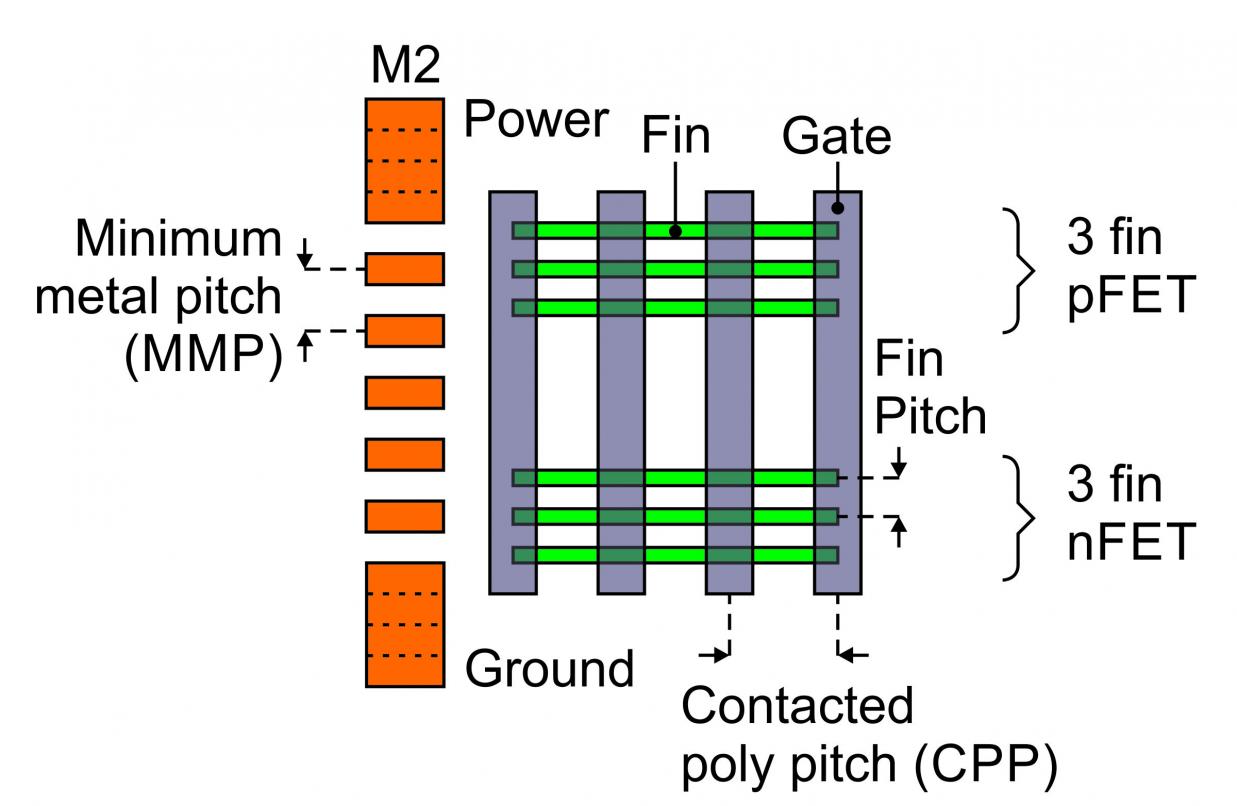

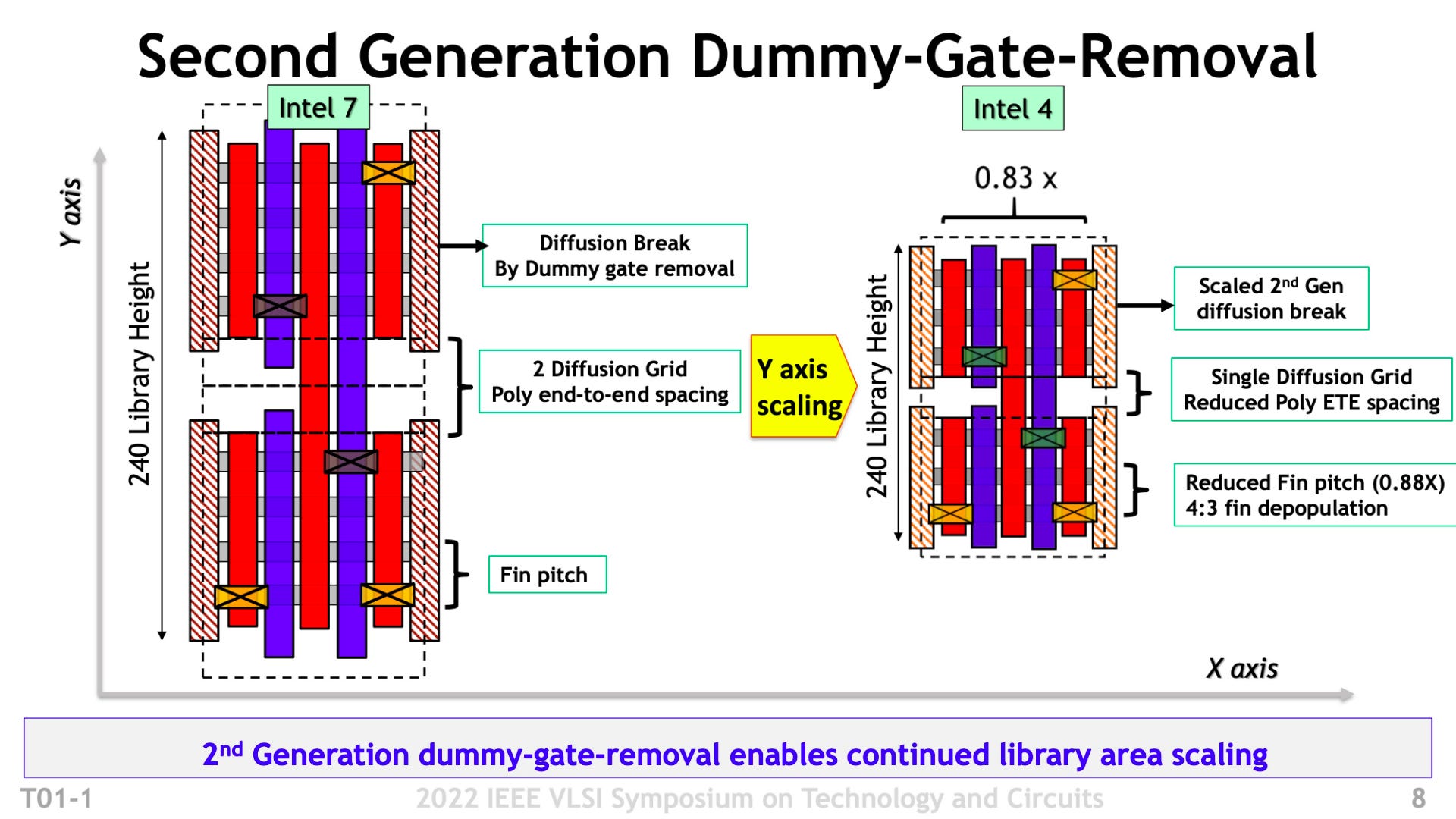

Scaling and Integration of High Speed Electronics and Optomechanical Systems : Scaling Challenges for Advanced CMOS Devices

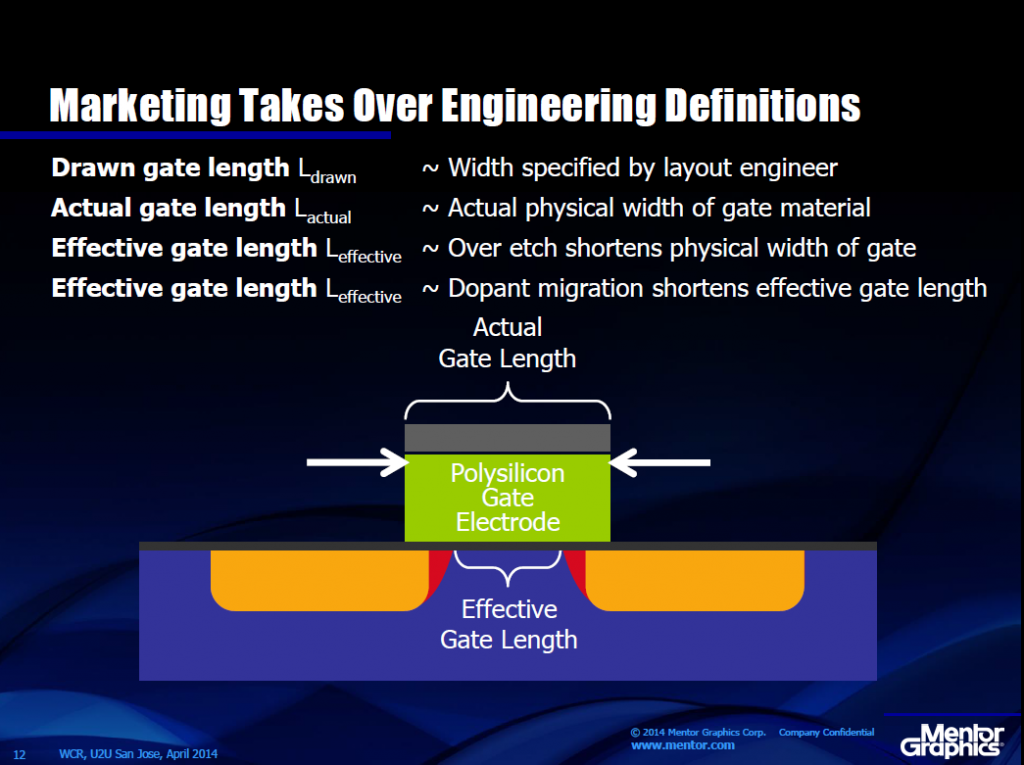

Analysis of the Relaxed Contacted-Poly-Pitch Effect on the RF Performance of Strained-SiGe-Channel p-FETs in 22nm FDSOI Technolo

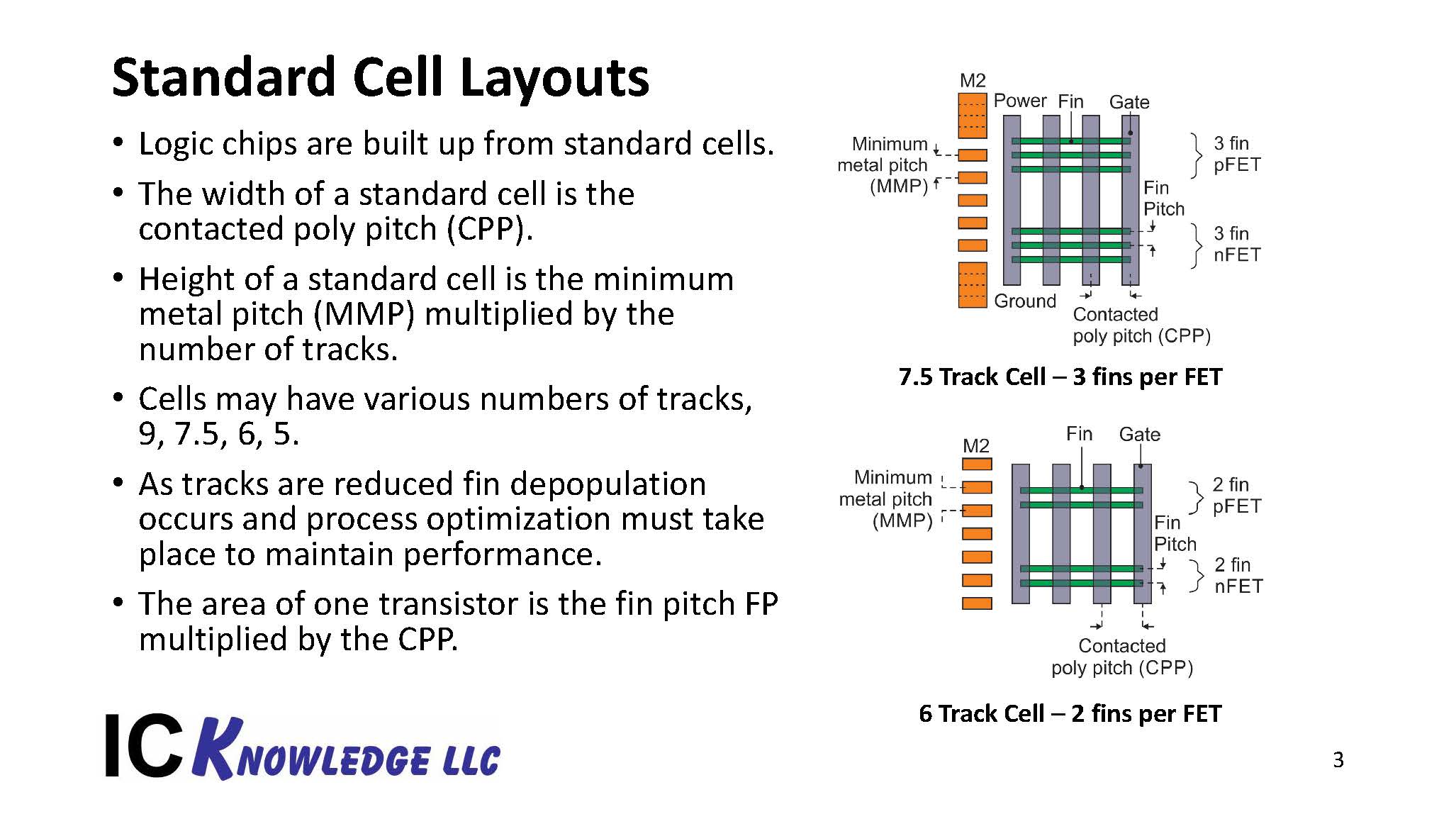

Figure A.1.2.1 Typical standard cell definitions. The cell height is... | Download Scientific Diagram